基础知识之一——STA基础概述

本文是DC笔记系列的第一篇,也是第一次来尝试写这种系列文章,有不足的地方非常欢迎同学们指出,该部分主要介绍什么是STA,有一个感性的认识,了解其使用的好处,什么地方再用,怎么用等。是基础部分的第一篇~主要分三个部分,什么是STA,CMOS数字设计中STA的使用于STA的局限性三个部分展开,参考《Static Timing Analysis for Nanometer Designs 》(第一章)的内容。

什么是STA

静态时序分析(简称STA)是用来验证数字设计时序的技术之一。下面将就时序与验证两个部分对STA进行一定的解释。

时序部分

简单介绍时序检查的内容及其优点。

时序检查的内容

时序检查是指建立时间与保持时间检查:建立时间检查是用来保证数据可以在给定时钟周期内到达触发器;保持时间检查是用来保证数据在被触发器采样后还能保持一定时间,即保证触发器不要漏采数据。

这些时序检查的目的都是为了保证触发器可以发送并且采样到正确的数据。

时序检查的优点

STA是一种可以验证设计中所有时序要求的详尽方法,而其他时序分析方法例如时序仿真则只能验证到被当前激励执行到的那部分时序路径。基于时序仿真的验证完备性取决于施加激励的完备性。如果使用时序仿真来验证一个千万门级别的设计,速度将会非常慢,并且实际上也无法充分验证。因此,想要基于时序仿真的方法来进行详尽的时序验证是非常困难的。

相比之下,STA则提供了一种更快更简单的方法去分析并检查设计中的全部时序路径。鉴于如今的ASIC设计规模已达千万门级别,STA已经成为了详尽地验证设计时序的必要方法。

验证的分类

动态仿真(时序仿真)

施加外部输入激励到所设计的电路模型,判断它所产生的输出响应是否符合预期功能,主要用于验证电路功能。施加一组激励,观察在这组激励下电路行为是否符合要求,然后换一组激励再重复以上过程,以此类推。

静态仿真

其对于设计的分析是静态地执行的,并不依赖于施加在输入端口上的激励

分析电路所有路径的时序,或者将待验证的电路与参考电路进行对照比较,主要用于验证电路性能指标,限于数字逻辑电路

物理验证

检查版图是否符合预定的设计规则,是否与电路一致

类型为DRC, ERC, LVS。设计规则检查(DRC, Design Rule Check)、 电气规则检查(ERC, Electronic Rule Check)、版图-原理图一致性检查(LVS, Layout Versus Schematic)

CMOS数字设计中STA的使用

SAT的对象

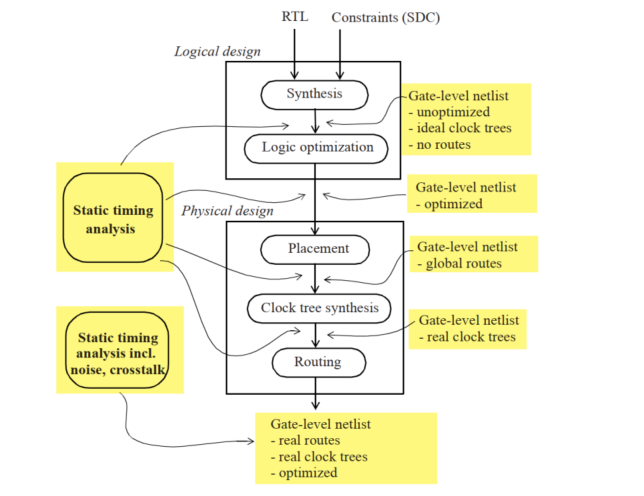

首先明确在设计流程中的位置,如下图所示

主要是对门级电路进行的静态时序分析。STA很少在RTL级完成,因为在这一抽象层级上,验证设计的功能更为重要,而非时序。 同样,由于块(block)的描述处于行为级,因此时序信息也并非都是可用的。可以结合检查的内容进行理解,只有综合出来寄存器以后才可以进行检查。简单来说就是门级网表。

但是,需要明确的是,作为一名IC设计工程师,你需要在写RTL代码的时候,就需要有一定的STA意识。更具体的内容后续会单独展开,该部分不属于本系列分析的内容。

不同阶段的STA

完成DC综合之后

- DC(Design Compiler)将RTL转化为门级网表,这个时候进行的STA是属于逻辑设计层次的静态时序分析。

- 这个阶段时钟为带有延时和抖动的理想时钟

- 这个阶段没有与布局有关的实际物理信息,因此假设这个阶段线延时也是理想的或者使用线负载模型来进行评估

完成布局

- 这个时候有了布局的信息,全局布线(global route)阶段

- 在物理设计的全局布线阶段,简化的布线用于估计布线长度,而对布线的估计用于确定计算走线延迟所需的电阻和电容值。 在此阶段中,无法考虑耦合效应带来的影响。

完成时钟树综合

- 这个时候的时钟是真实的时钟树

完成布线

- 最终布线(final route)阶段,在实际精细的布线完成后,就可以提取实际的RC值,并且可以分析耦合效应带来的影响这个时候使用的是真实的时钟树,布局布线。提取工具用于从布线设计中提取详细的寄生参数(RC值),这样的提取工具一般具有以下选项:在迭代优化期间以较少的运行时间和较低精确度的RC值来获取寄生参数,以及在最终验证期间以较长的运行时间来提取非常精确的RC值。

总结

在逻辑级(未进行物理设计的门级),STA可采用以下模型:

- 理想的互连线或者基于线负载模型的互连线

- 带有延迟和抖动估计值的理想时钟

在物理设计阶段,除了上述模型,STA还可采用以下模型:

- 具有近似估计值的全局布线的互连线、具有近似寄生参数提取值的实际布线的互连线、具有可以签收(signoff)精度寄生参数提取值的实际布线的互连线

- 实际的时钟树

- 包括串扰的影响或者不包括串扰的影响

STA的局限性

这里的局限性可以理解为STA不能做的,经过后续的学习,也可以从本质上理解为什么不能处理这些问题,相关的内容将会在下节展开~

跨时钟周期的功能行为:STA无法建模或仿真跨时钟周期变化的功能行为

IO接口时序:可能仅根据STA约束无法规定IO接口要求。例如,设计人员可能使用SDRAM仿真模型为DDR接口选择详细的电路级仿真

未知态X的处理:STA技术仅处理逻辑0和逻辑1(或高电平/低电平)的逻辑域,或者是上升沿和下降沿的逻辑域。 设计中的未知态X导致不确定的值在整个设计中传播,这也是无法使用STA进行检查。

PLL设置:PLL的配置可能未被正确加载或设置

跨异步时钟域

FIFO指针不同步

跨时钟周期的功能行为

伪路径(false path):当系统应用程序从不使用此类路径时,或者在时序违例路径的敏感列表中使用了互斥的条件时,可能会发生这种情况。 这种时序路径被称为伪路径,因为这种时序路径实际上不会被执行。

当在设计中指定了正确的时序约束(包括伪路径和多周期路径约束)时,STA结果的质量会更好。 在大多数情况下,设计人员可以利用设计的固有知识并指定约束条件,以便在STA期间消除伪路径。

模拟模块和数字模块之间的接口:由于STA不处理模拟模块,因此验证方法需要确保这两种类型的模块之间的连接正确。

复位顺序:检查所有触发器在异步或同步复位后是否都复位为所需的逻辑值,这是无法使用静态时序分析来检查的。