dc_labs--lab1的学习与总结

本节为dc_labs系列的第一篇,主要根据自己对于lab的理解,简述实验的过程,同时对于笔者自己觉得需要进一步理解的进行总结学习。本节重点在于理解启动文件与DC的综合流程。建议与对应博文(DC学习笔记正式篇之零——综述与基本流程介绍)进行结合起来进行学习。该文为对应部分的实践篇的内容。本系列博文不会只是带着进行实验内容,个人觉得单纯跑一遍实验意义不大。会结合自己学习的理解进行部分展开。有问题欢迎留言一起学习。同时会对lab的内容进行一定的简化,完整的lab_guide(笔者已经进行了简单的翻译)请加入QQ群获取。

实验目标

1,通过该实验可以学会配置DC的启动文件,同时对其中的配置部分进行理解学习

2,理解DC做综合的流程,在topo拓扑模式下完成综合,体验synthesis flow

3,学会自己获取DC的帮助界面进行相关命令的查询

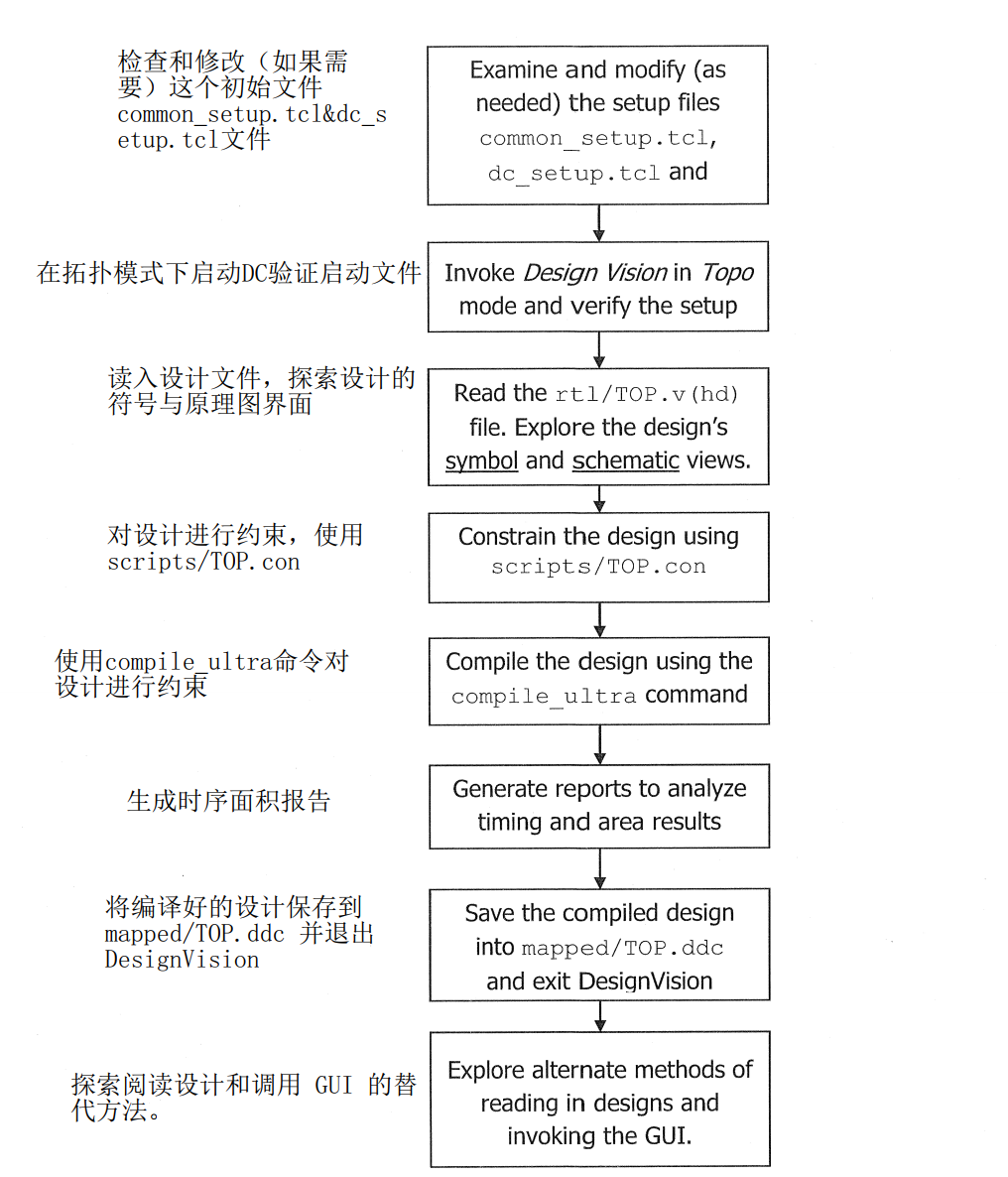

实验流程

该实验流程简单的对DC综合进行了一个概述,简单来说就是设置dc的启动文件,然后读入设计,读入约束,综合,生成报告,写入编译好的文件并保存,退出。这只是一个很top层的一个理解,重点在于清楚这些步骤,以及简单了解这些步骤是做什么就可以了,后续对于每一步,都有相关的实验。了解一个完整的过程,后续在一点点的深入。

对于该部分的重点这里再赘述一遍,理解启动文件的内容是什么,尽可能的学习自己进行相关文件的配置,其次是学习体验整个综合流程,最后是学会自己使用帮助命令查询自己需要理解的指令

实验步骤

任务1,查看浏览启动文件

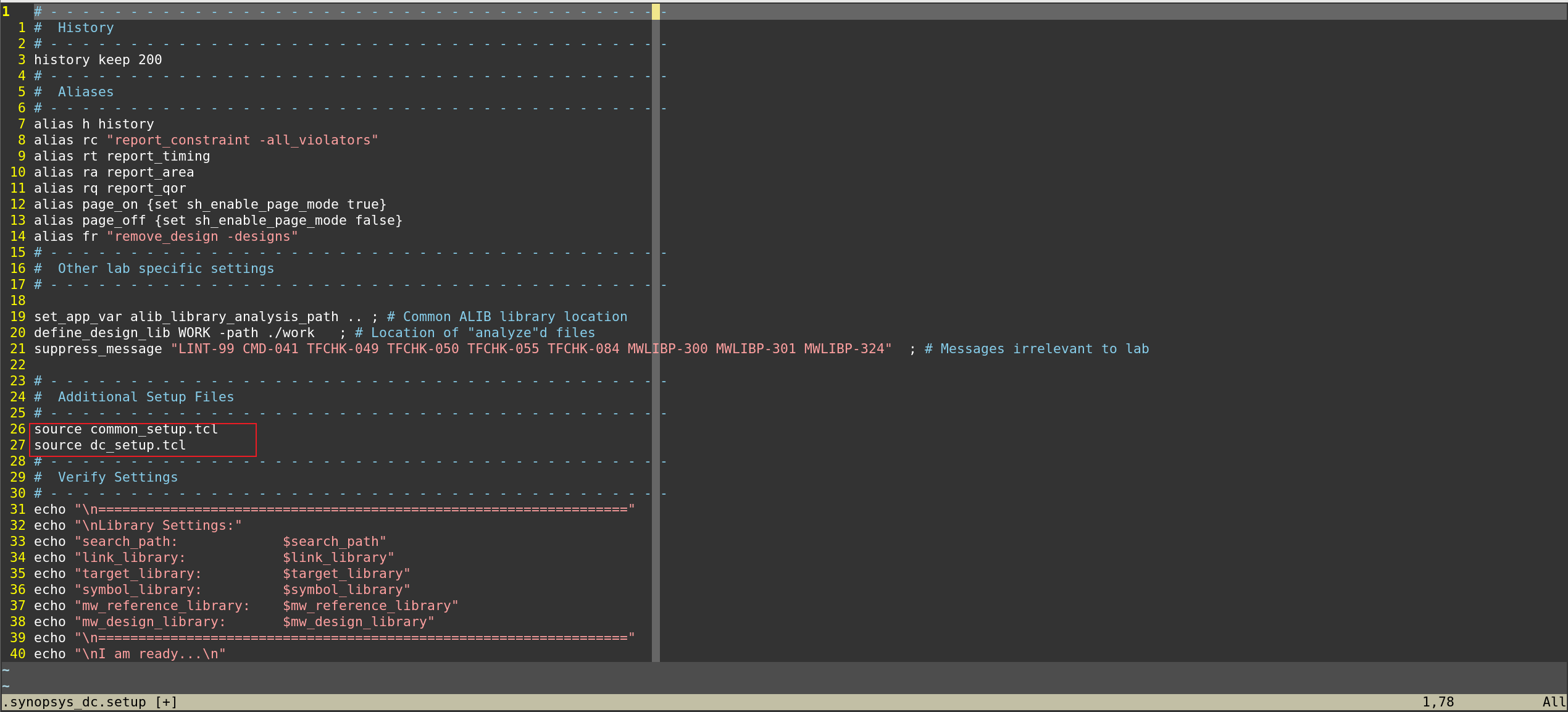

进入lab1的目录,然后查看启动文件.synopsys_dc.setup文件

cd lab1 |

我们可以看到对应的内容如下,其中重点在于source的两个文件,其余设置并不是必须的。aliases相当于别名的设置,history设置保存历史命令的条数,suppress_message用来屏蔽相关的警告信息

第一个是common_setup.tcl。另一个是dc_setup.tcl文件,我们分别打开两个文件来看其中的内容。

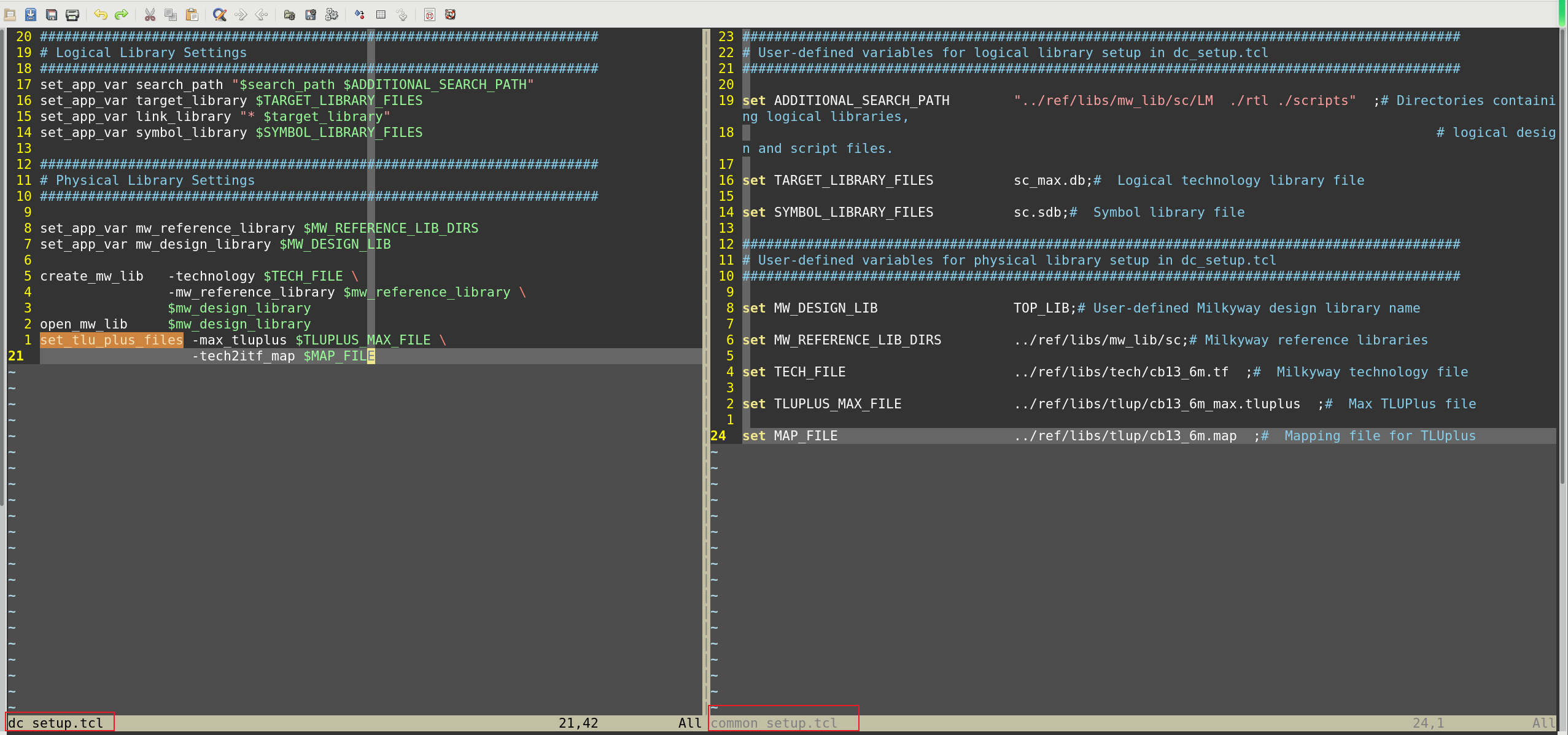

更详细的库的设置说明在DC学习笔记正式篇之零——综述与基本流程介绍已经进行了解释,这里进行概述性的解释,其中左边的common文件就是对于一些变量进行定义,然后再dc_setup中调用进行设置,因此source的顺序也是有先后的。对其中的解释如下:

- search_path 搜索路径。顾名思义就是用来查找相关需要使用的工艺库呀,设计文件,脚本等

- target_library 目标库/工艺库 指定工艺库的名称,是综合后电路网表要最终映射到的库

- link_library 链接库 link_library 设置模块或者单元电路的引用,对于所有 DC 可能用到的库,我们都需要在link_library 中指定,一般与target_library相同

- symbol_library 符号库 symbol_library 是定义了单元电路显示的 Schematic 的库。用户如果想启动design_analyzer 或 design_vision 来查看、 分析电路时需要设置 symbol_library。

- create_mw_lib 创建一个mw库文件,这里的库名称是

$mw_design_library(实际上是变量设置的TOP_LIB)- create_mw_lib的直接参数是设计库名称

-technology 指定的参数是工艺库名称

-mw_reference_library 指定的参数是参考库名称。 - 其中,Synopsys使用一个统一的Milkyway database可以在Synopsys Galaxy™Design Platform中所有的EDA工具之间进行数据交换,避免了工具之间文件格式转换的大量时间花费,文件之间语义不匹配造成的信息丢失等问题。Design Compiler可以write_milkyway一个mapped之后的Milkyway database IC Compiler从Milkyway database中读取设计信息和库信息,然后执行placement, clock tree synthesis和 routing。也可以将不同阶段的设计信息再保存为Milkyway database。若tluplus文件没有时,可由foundry给的.itf转成tluplus。使用的是Synopsys公司的star_RC.

- create_mw_lib的直接参数是设计库名称

- set_tlu_plus_files 设置寄生参数库。寄生RC查找表,ICC使用网络几何形状以及该文件来计算互联电阻电容。若tluplus文件没有时,可由foundry给的.itf转成tluplus。使用的是Synopsys公司的star_RC.

这里解释一些为什么还需要这些Milkyway相关的设置,这里使用的综合是dc在topo模式下的综合,已经有了相对严格真实的延时,而不需要使用线负载模型中的延时参数,会使得综合时序更接近真实情况。一般在自己实验阶段compile就已经可以了,这里我们需要使用的编译命令是compile_ultra。

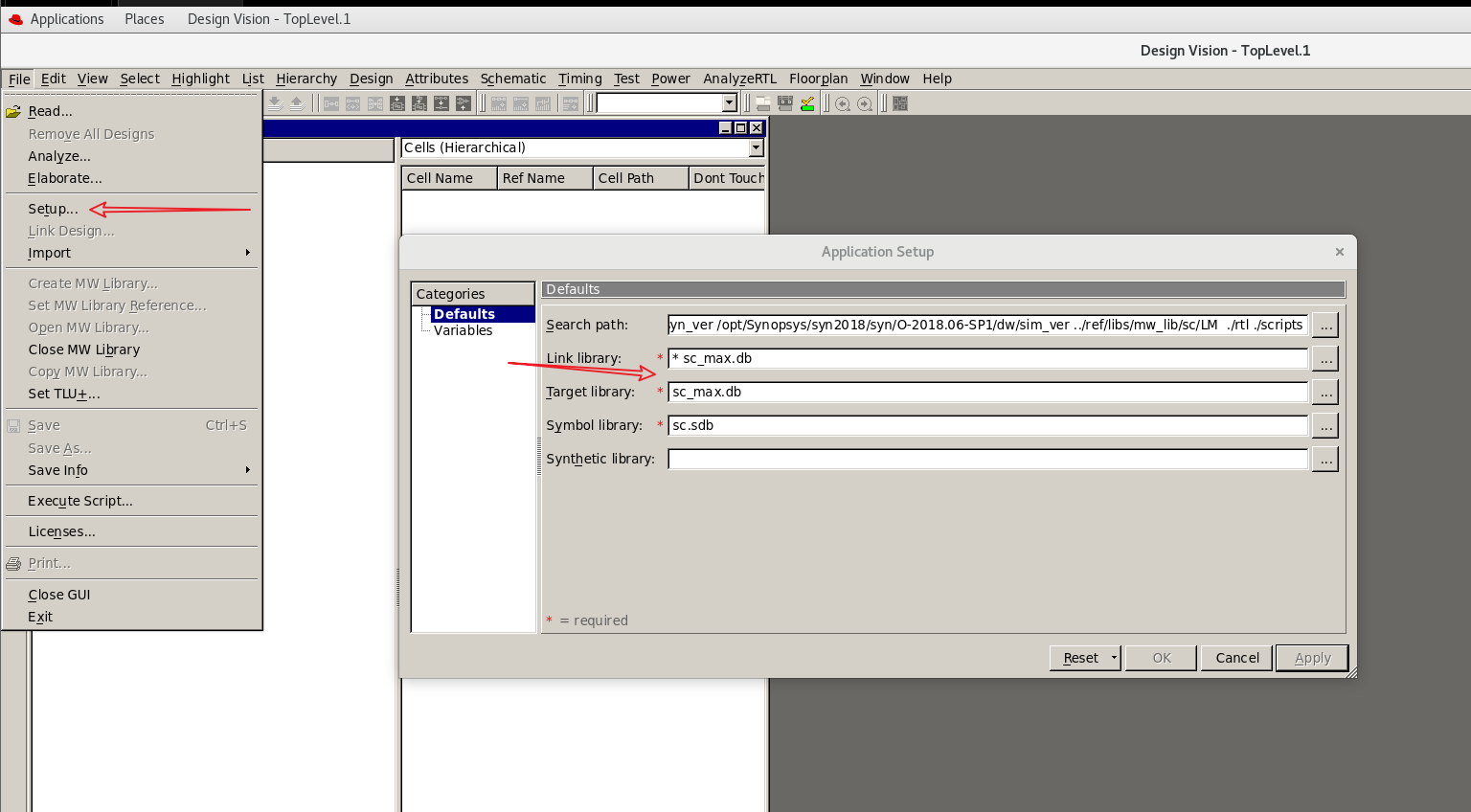

任务2,启动DC,检查启动文件加载情况

我们前面介绍dc在启动时候会加载启动文件,这里启动DC以后进一步检查DC是否已经正确设置了我们启动文件中指定的路径以及相关库的信息。输入 dc_shell -topo,看到如下打印信息,由于我并不是第一次打开,会出现 Error: Library 'TOP_LIB' already exists. (MWUI-004)可以忽略。可以看到已经进入了topo模式,然后输入gui_start就可以看到弹出来的GUI界面了。

[icer@ICer lab1]$ dc_shell -topo |

1,检查set_up项的内容

查看是否与设置的启动文件中的内容一致

2,在命令行进行对应的检查

printvar target_library |

输出如下:

dc_shell-topo> printvar target_library |

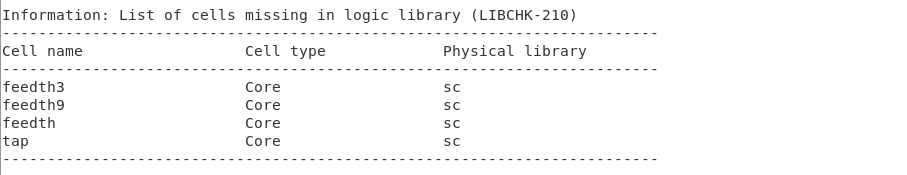

3,检查逻辑库和物理库之间的一致性

check_library |

请注意,检查报告逻辑库中缺少 4 个单元格。有一个表格列出了缺少的单元格。它们是“馈通”和“分接单元”,在物理布局中是必需的,但在逻辑设计中不需要(也称为“仅物理”单元)。因此可以忽略警告。输出如下

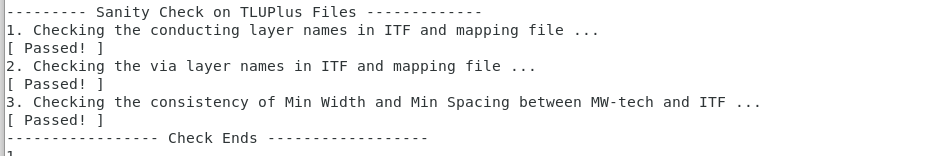

4,检查 TLUPus 和技术文件之间的一致性

check_tlu_plus_files |

看到三个pass信息。

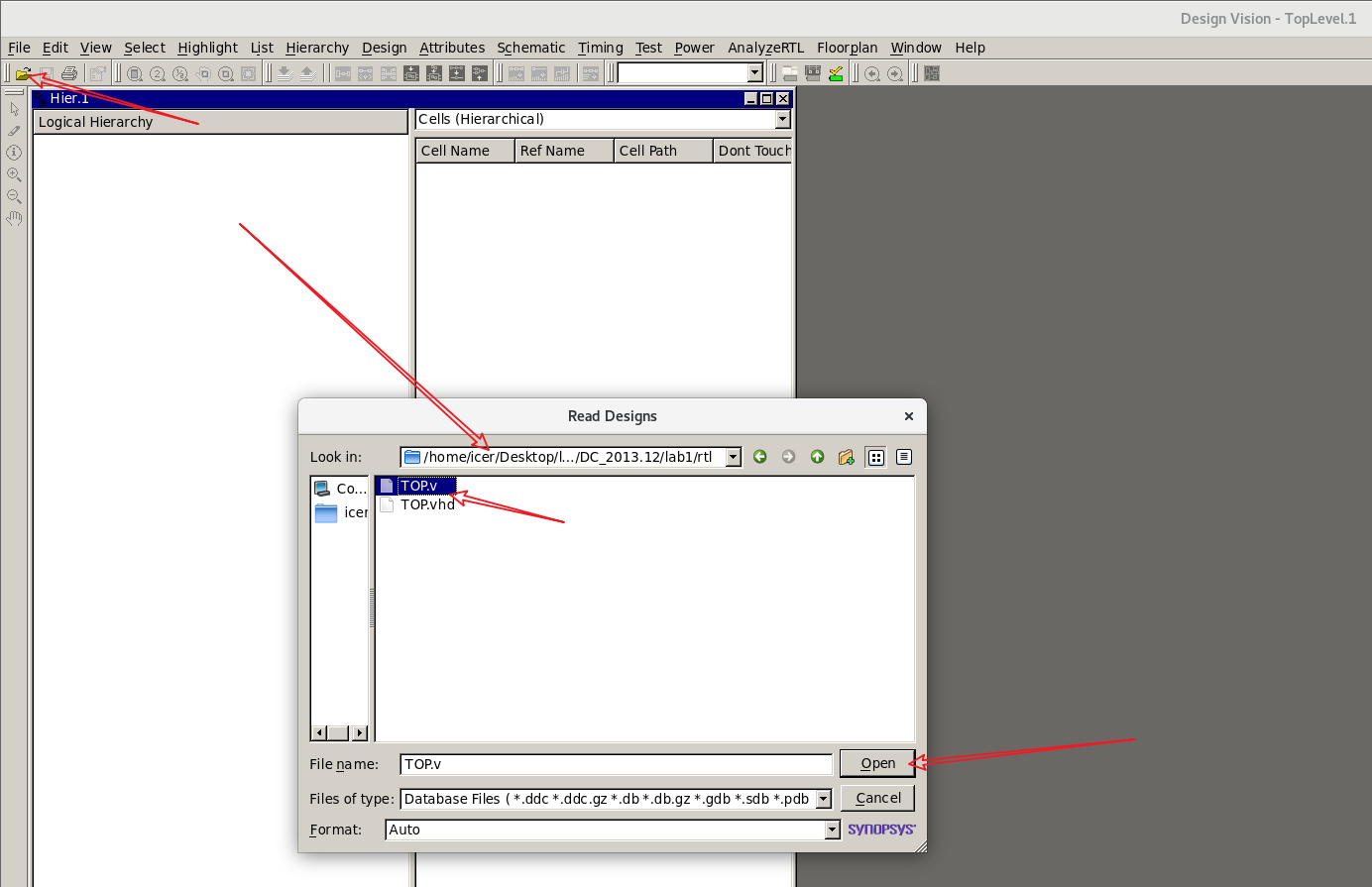

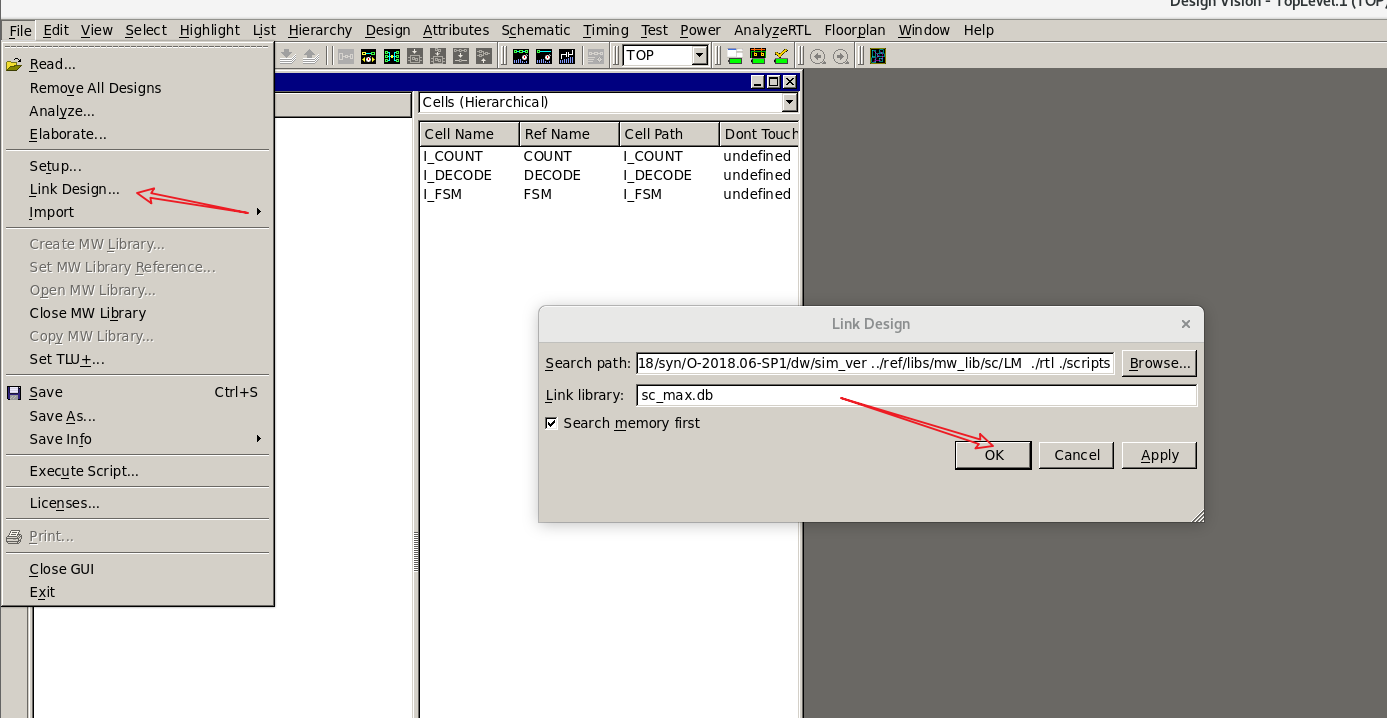

任务3,读入设计文件,写入unmapped文件

1,读入设计

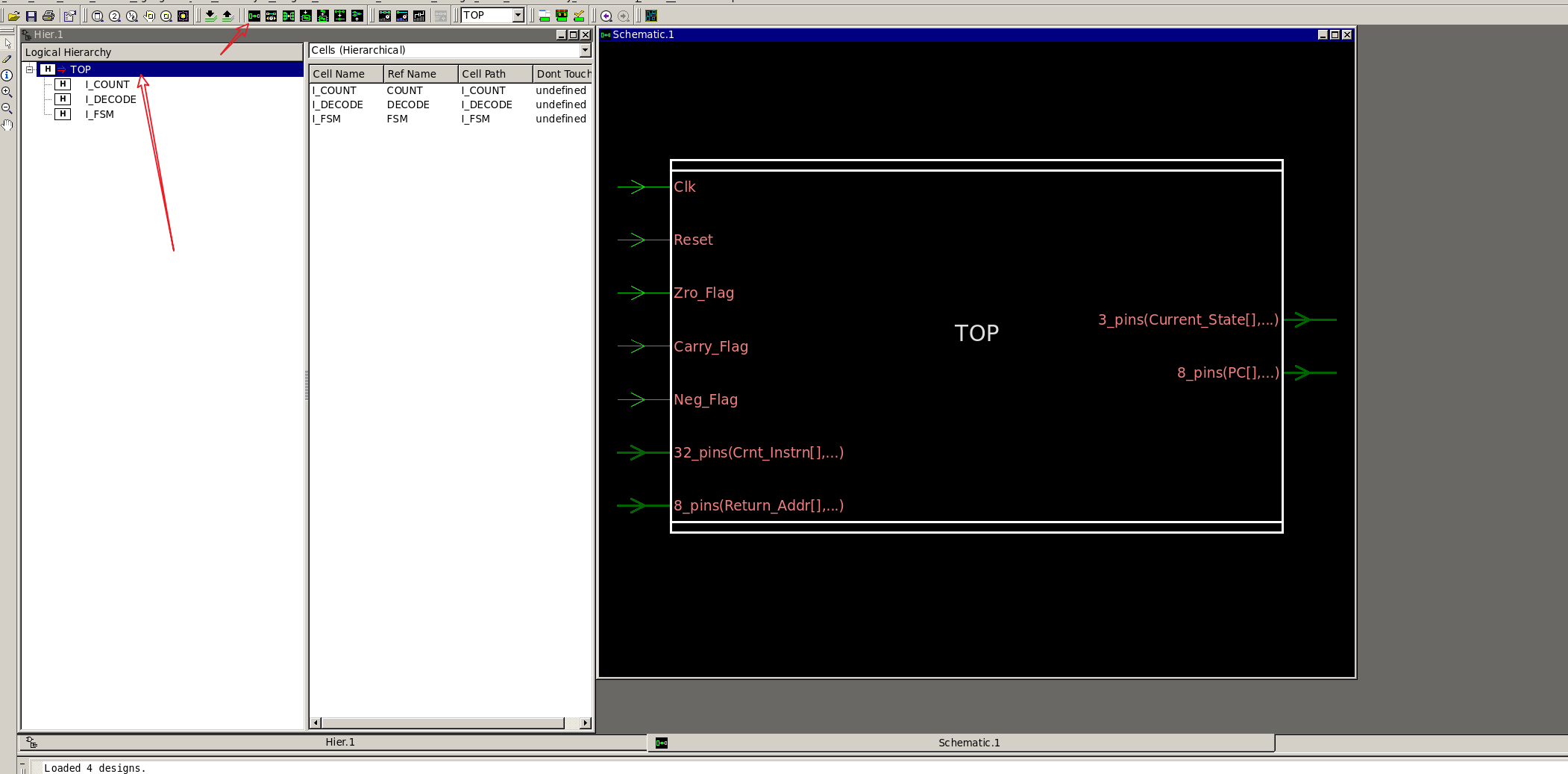

在GUI界面读入设计文件。成功以后link设计。

命令行与log栏打印的成功信息如下

dc_shell-topo> link |

可以打开原理图,进行相关的探索。这里不进行详述,可以查看lab_guide相关内容,鼠标点开查看其标准单元为GRTCH的形式。同时是有逻辑层次的,注意可以和综合后进行对比。

2,写入unmapped文件

write -hier -f ddc -out unmapped/TOP.ddc |

打印信息如下

dc_shell-topo> write -hier -f ddc -out unmapped/TOP.ddc |

查看dc内存中的设计与库文件

list_designs |

打印结果如下

dc_shell-topo> list_designs |

任务4,约束设计&编译

1,约束设计

source scripts/TOP.con |

打印信息如下

dc_shell-topo> source scripts/TOP.con |

这里对于其中的约束内容不进行介绍,后续会有更详细的分析。

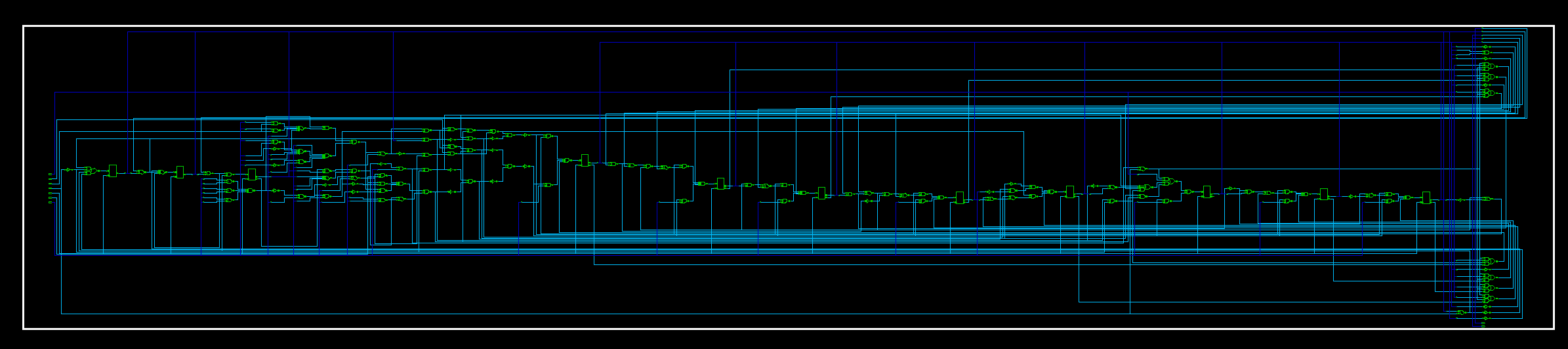

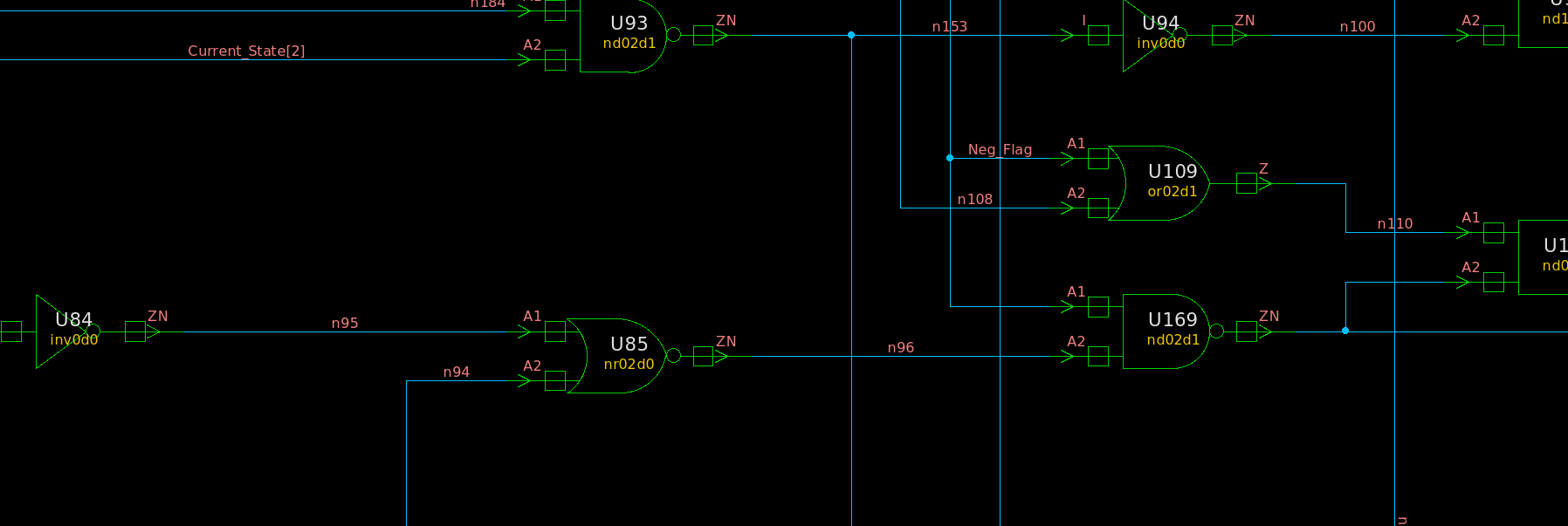

2,编译

compile_ultra |

等待编译完成。在编译过程中监控日志。您将看到编译的不同优化阶段的各种表格。 “AREA”栏表示设计尺寸。 “WORST NEG SLACK”列指示设计中的关键或最差路径违反了多少,相对于其约束(实际延迟 - 预期延迟)。 “TOTAL NEG SLACK”是所有违反路径松弛的总和。当优化达到“收益递减”点,或者松弛数达到零时,这意味着设计中没有违反时序路径,compile_ultra结束。compile ultra 已自动展平或“取消分组”子设计 DECODE、FSM 和 COUNT,以生成最佳时序和面积结果。这里的原理图中的标准单元就已经不是GETCH的形式了。

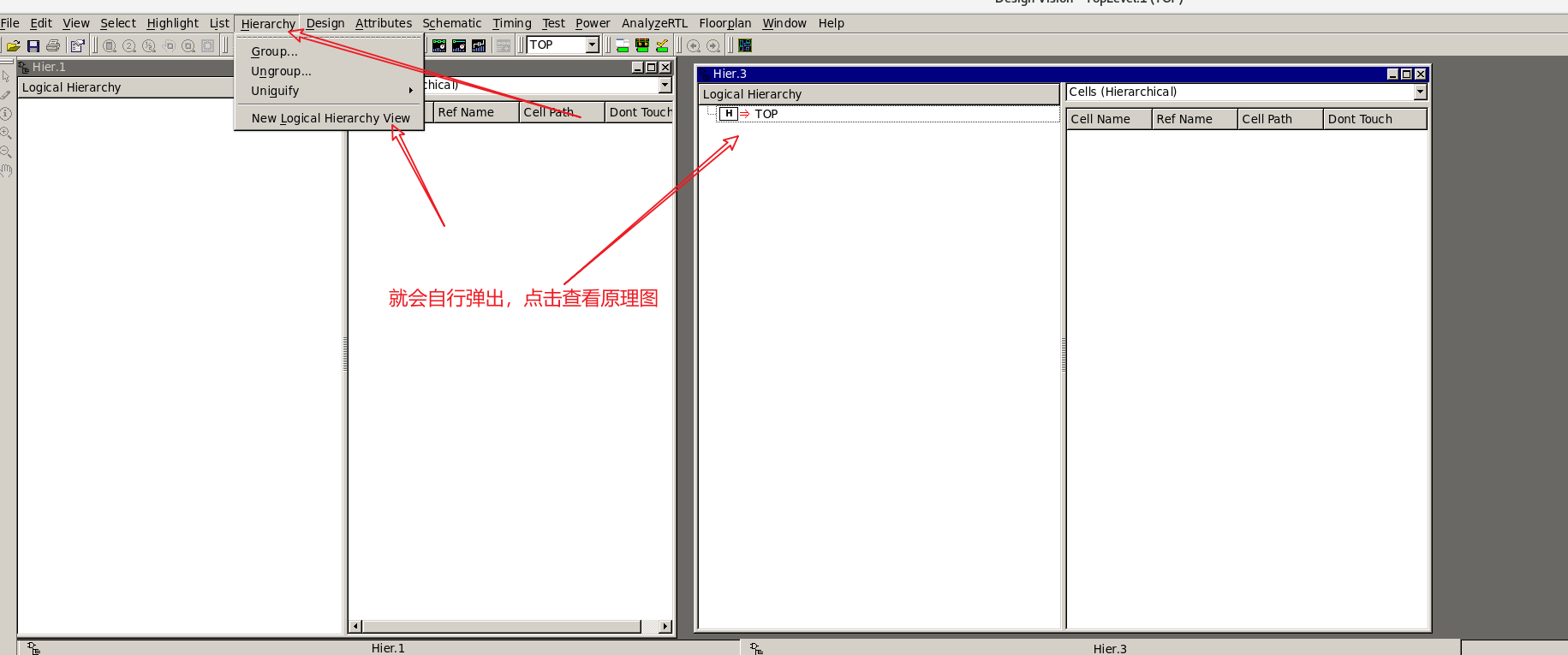

这里笔者综合以后,原本的界面就会消失,需要重新打开。

注意如下是TOP层,已经没有层次划分了。

使用滚轮将其放大,看到,其中的标准单元已经不是GETCH的形式了。而是目标库里的。

任务5,查看报告并写入保存综合后的文件。

1,写入编译好的文件

write -hierarchy -format ddc -output /home/icer/Desktop/lab/dc_lab/DC_2013.12/lab1/unmapped/TOP.ddc |

也可以使用图形化的界面进行保存,选择TOP,选择file->save as,选择保存的目录即可。

2,查看报告

rc |

其对应的意义在alias中已经进行定义,可以自行查看。

alias rc "report_constraint -all_violators" |

键入exit退出dc。

exit |

任务6,执行脚本与获取帮助

1,执行脚本

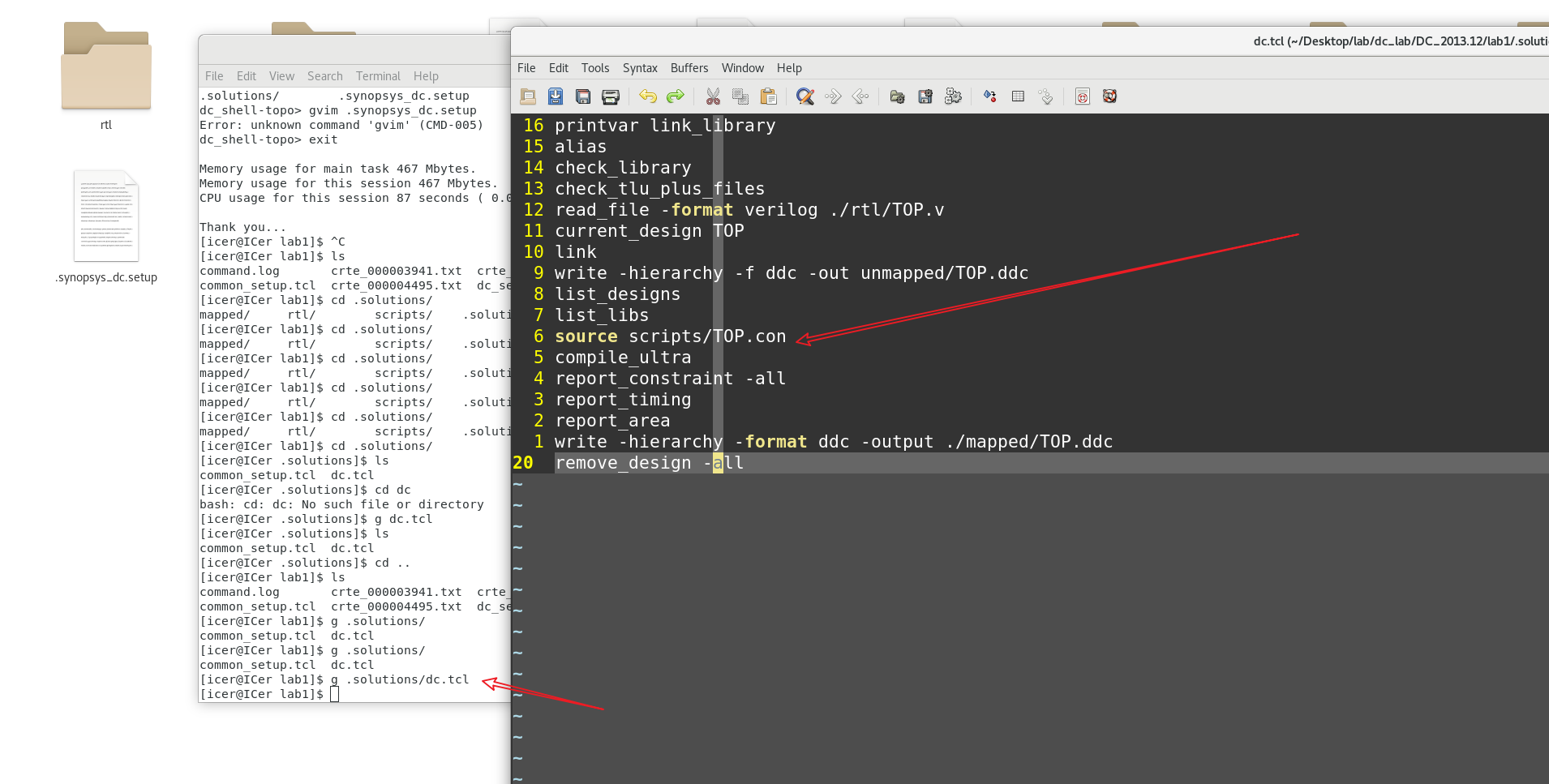

我们前面就是将命令一步一步输入的,也可以直接执行脚本来一步操作以上所有步骤,这里我们直接使用solution里提供的脚本即可。.solution相当于答案,里边有对应的脚本,查看脚本,如下图所示,这里需要对source TOP.con的位置进行修改。

然后执行

dc_shell -topo -f .solutions/dc.tcl | tee dc.log |

等待编译结束即可。

2,获取帮助

假设我们需要查找带有clock的命令。先使用如下命令进行查找:

help *clock* |

输出结果如下:

dc_shell-topo> help *clock* |

假设我们需要查看all_clock这条命令,输入如下命令即可:

man all_clocks |

这里的man就是manual,手册的意思。就可以查看相关命令的解释举例等相关信息。